River Publishers Series in Communications and Networking

# Advancing Edge Artificial Intelligence **System Contexts**

**Editors:**

Ovidiu Vermesan **Dave Marples**

# RIVER PUBLISHERS SERIES IN COMMUNICATIONS AND NETWORKING

Series Editors:

#### ABBAS JAMALIPOUR

The University of Sydney, Australia

#### MARINA RUGGIERI

University of Rome Tor Vergata, Italy

The "River Publishers Series in Communications and Networking" is a series of comprehensive academic and professional books which focus on communication and network systems. Topics range from the theory and use of systems involving all terminals, computers, and information processors to wired and wireless networks and network layouts, protocols, architectures, and implementations. Also covered are developments stemming from new market demands in systems, products, and technologies such as personal communications services, multimedia systems, enterprise networks, and optical communications.

The series includes research monographs, edited volumes, handbooks and textbooks, providing professionals, researchers, educators, and advanced students in the field with an invaluable insight into the latest research and developments.

Topics included in this series include:

- Communication theory

- Multimedia systems

- · Network architecture

- Optical communications

- Personal communication services

- · Telecoms networks

- Wi-Fi network protocols

For a list of other books in this series, visit www.riverpublishers.com

# Advancing Edge Artificial Intelligence System Contexts

# **Editors**

Ovidiu Vermesan

SINTEF, Norway

**Dave Marples**

Technolution B.V., The Netherlands

Published, sold and distributed by: River Publishers Alsbjergvej 10 9260 Gistrup Denmark

www.riverpublishers.com

ISBN: 978-87-7004-102-7 (Hardback) 978-87-7004-101-0 (Ebook)

©The Editor(s) (if applicable) and The Author(s) 2023. This book is published open access.

#### **Open Access**

This book is distributed under the terms of the Creative Commons Attribution-Non-Commercial 4.0 International License, CC-BY-NC 4.0 (http://creativecommons.org/licenses/by/4.0/), which permits use, duplication, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, a link is provided to the Creative Commons license and any changes made are indicated. The images or other third party material in this book are included in the work's Creative Commons license, unless indicated otherwise in the credit line; if such material is not included in the work's Creative Commons license and the respective action is not permitted by statutory regulation, users will need to obtain permission from the license holder to duplicate, adapt, or reproduce the material.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper.

#### **Dedication**

"The test of a first-rate intelligence is the ability to hold two opposed ideas in the mind at the same time and still retain the ability to function."

- F. Scott Fitzgerald

"The world needs dreamers, and the world needs doers. But above all, what the world needs most are dreamers that do."

- Sarah Ban Breathnach

"The real question is, when will we draft an artificial intelligence bill of rights? What will that consist of? And who will get to decide that?"

- Gray Scott

"The greatest masterpiece in literature is only a dictionary out of order."

- Jean Cocteau

"There's a way to do it better. Find it."

- Thomas Edison

#### Acknowledgement

The editors would like to thank all the contributors for their support in the planning and preparation of this book. The recommendations and opinions expressed in the book are those of the editors, authors, and contributors and do not necessarily represent those of any organizations, employers, or companies.

Ovidiu Vermesan Dave Marples

# **Contents**

| C  | onten        | ts                   |                                                                                                       | VII                        |

|----|--------------|----------------------|-------------------------------------------------------------------------------------------------------|----------------------------|

| Pr | eface        |                      |                                                                                                       | xiii                       |

| Li | st of 1      | Figures              |                                                                                                       | xv                         |

| Li | st of T      | <b>Fables</b>        |                                                                                                       | xix                        |

| Li | st of (      | Contrib              | itors                                                                                                 | xxi                        |

| Li | st of A      | Abbrevi              | ations                                                                                                | xxiii                      |

| 1  | Ovid<br>Jani | liu Vern<br>s Judvai | Ra Mesh Technologies<br>esan, Kai vorm Walde, Roy Bah<br>tis, Gatis Gaigals, Tore Karlsen<br>tik Sand | _                          |

|    | 1.1<br>1.2   | Introd               | ew of the State-of-the-Art Wirel Mesh components and roles Wireless routing concepts                  | less Mesh Technologies 5   |

|    | 1.3          |                      | g protocols                                                                                           | ector (AODV) 9<br>DLSR) 10 |

|    |              | 1.3.4                | 1.3.5.2 Bluetooth Low Ener<br>1.3.5.3 OpenThread and Th                                               | 12                         |

|   |      | 1.3.5.5 Wi-Fi                                            | 16 |

|---|------|----------------------------------------------------------|----|

|   |      | 1.3.5.6 Wi-SUN                                           | 18 |

|   |      | 1.3.5.7 WirelessHART                                     | 18 |

|   |      | 1.3.5.8 Z-WAVE                                           | 2( |

|   |      |                                                          | 21 |

|   | 1.4  | LoRa and LoRaWAN Technology                              | 22 |

|   |      | 1 2                                                      | 22 |

|   |      | 1.4.2 LoRaWAN protocol                                   | 24 |

|   |      |                                                          | 26 |

|   | 1.5  | LoRa Mesh and Enabling AI Technologies                   | 27 |

|   | 1.6  | Applications for LoRa Mesh                               | 28 |

|   | 1.7  | Conceptual Edge AI and LoRa Mesh Device Architecture     | 28 |

|   |      |                                                          | 29 |

|   |      | 1.7.2 AI accelerators                                    | 29 |

|   |      | 1.7.3 2.4 GHz LoRa and Bluetooth radios                  | 3( |

|   |      | ±                                                        | 3( |

|   |      | *                                                        | 3( |

|   |      |                                                          | 31 |

|   |      |                                                          | 31 |

|   |      | $\mathcal{C}$                                            | 31 |

|   |      |                                                          | 32 |

|   |      | **                                                       | 32 |

|   | 1.8  |                                                          | 32 |

|   | 1.9  | Discussion and Conclusions                               | 35 |

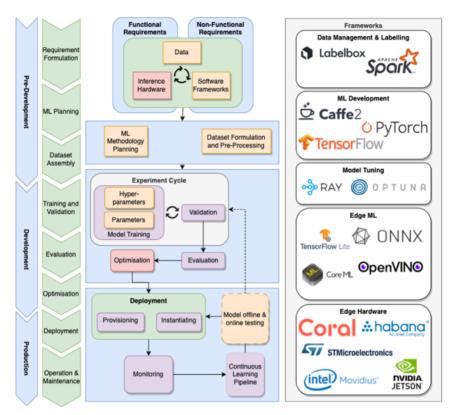

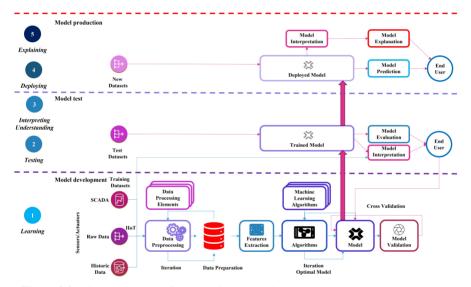

| 2 | Edg  | e AI Lifecycle Management                                | 43 |

|   | _    | Purice, Francesco Barchi, Thorsten Röder, and Claus Lenz |    |

|   | 2.1  | Introduction and Background                              | 43 |

|   | 2.2  | Pre-development                                          | 46 |

|   | 2.3  |                                                          | 49 |

|   | 2.4  |                                                          | 58 |

|   | 2.5  |                                                          | 60 |

| 3 | Fede | erated Learning: Privacy, Security and Hardware          |    |

|   |      |                                                          | 65 |

|   |      | y Yassine Abidi, Iyad Dayoub, Elhadj Doguech,            |    |

|   |      | Ihsen Alouani                                            |    |

|   | 3.1  | Introduction and Background                              | 66 |

|   | 3.2  |                                                          | 67 |

|   |       |               |                                              | Contents | ix  |

|---|-------|---------------|----------------------------------------------|----------|-----|

|   |       | 3.2.1         | Horizontal Federated Learning                |          | 68  |

|   |       | 3.2.2         | Vertical Federated Learning                  |          | 68  |

|   |       | 3.2.3         | Federated Transfer Learning                  |          | 69  |

|   | 3.3   |               | nges and Limitations of Federated Learning.  |          | 69  |

|   | 0.0   | 3.3.1         | Security challenge                           |          | 69  |

|   |       | 0.0.1         | 3.3.1.1 Malicious Clients                    |          | 70  |

|   |       |               | 3.3.1.2 Mitigating client-based attacks .    |          | 71  |

|   |       |               | 3.3.1.3 Malicious Server attacks and mitig   |          | 73  |

|   |       | 3.3.2         | Privacy challenge                            |          | 74  |

|   |       | 3.3. <b>2</b> | 3.3.2.1 Client privacy attacks               |          | 75  |

|   |       |               | 3.3.2.2 Mitigating client-based attacks .    |          | 76  |

|   |       |               | 3.3.2.3 Server based privacy attacks         |          | 77  |

|   |       | 3.3.3         | Hardware constraint and opportunities        |          | 79  |

|   | 3.4   | Conclu        |                                              |          | 82  |

|   |       | 0011411       |                                              |          | -   |

| 4 | Insi  | de the A      | A Accelerators: From High Performance to     | Energy   |     |

|   | Effic | ciency        |                                              |          | 87  |

|   | Ana   | Pinzari,      | Adrien Prost-Boucle, Christelle Rabache,     |          |     |

|   | and   | Frédério      | c Pétrot                                     |          |     |

|   | 4.1   | Introdu       | action and Background                        |          | 87  |

|   | 4.2   | Relate        | d Work                                       |          | 89  |

|   | 4.3   | Classif       | fication Model                               |          | 90  |

|   | 4.4   | Quanti        | zation                                       |          | 91  |

|   | 4.5   |               | ments and Results                            |          | 93  |

|   |       | 4.5.1         | Time and power consumption                   |          | 94  |

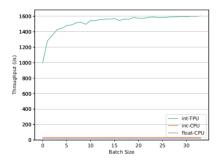

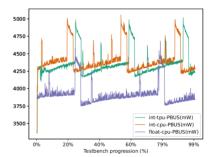

|   |       |               | 4.5.1.1 Google Coral Board                   |          | 95  |

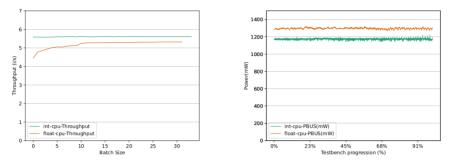

|   |       |               | 4.5.1.2 STM32MP1 Board                       |          | 96  |

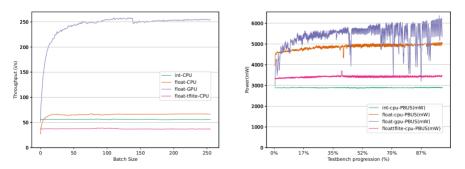

|   |       |               | 4.5.1.3 NVIDIA Jetson                        |          | 96  |

|   |       | 4.5.2         | FPGA                                         |          | 97  |

|   |       |               | 4.5.2.1 QKeras Library                       |          | 97  |

|   |       |               | 4.5.2.2 Quantized model and Experimenta      |          | 99  |

|   | 4.6   | Conclu        | ision                                        |          | 100 |

| 5 | Deci  | anina I       | ightweight CNN for Images: Architectural     |          |     |

|   |       |               | s and Techniques                             |          | 105 |

|   |       | -             | rd, Lucas Mohimont, and Luiz Angelo Steffene |          | 100 |

|   | 5.1   |               | action and Background                        |          | 106 |

|   | 5.2   | CNNs          |                                              |          | 108 |

|   | ٠.٧   | 5.2.1         | The pioneers                                 |          | 108 |

|   |       | J1            | Promotio                                     |          | 100 |

| ents |

|------|

| ents |

|   |      | 5.2.2    | YOLO, first step towards fast object detectors    | 109 |

|---|------|----------|---------------------------------------------------|-----|

|   |      | 5.2.3    | Convolutional Neural Network architecture         |     |

|   |      |          | improvements                                      | 111 |

|   |      | 5.2.4    | Tackling memory consumption                       | 113 |

|   |      | 5.2.5    | Structural re-parameterization                    | 113 |

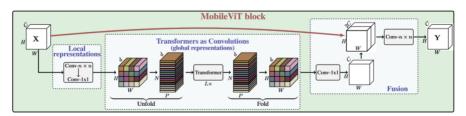

|   | 5.3  | Transf   | Formers for EdgeAI                                | 116 |

|   |      | 5.3.1    | Hybrid transformers                               | 116 |

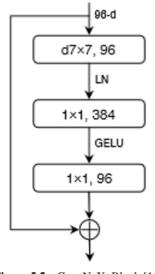

|   | 5.4  | ConvN    | NeXts                                             | 119 |

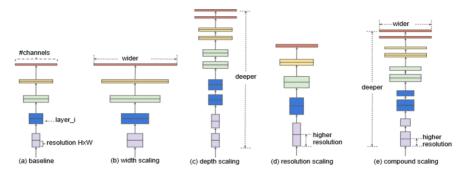

|   | 5.5  | Neura    | l Architecture Search                             | 120 |

|   |      | 5.5.1    | NAS scale study                                   | 121 |

|   | 5.6  | Concl    | usion                                             | 123 |

| 6 | Nati | ural La  | nguage Conditioned Planning of Complex Robotics   |     |

|   | Task | KS       |                                                   | 131 |

|   | Tom  | s Eduar  | ds Zinars, Oskars Vismanis, Peteris Racinskis,    |     |

|   | Jani | s Arents | s, and Modris Greitans                            |     |

|   | 6.1  | Introd   | uction                                            | 131 |

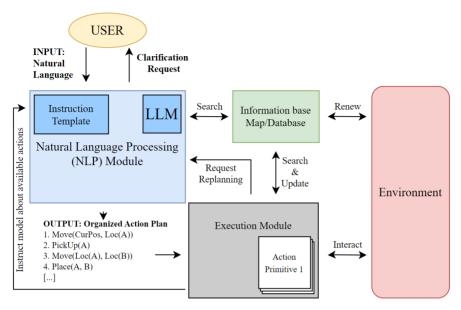

|   | 6.2  |          | al Language Processing for Robotics               | 133 |

|   |      | 6.2.1    | Large language models                             | 133 |

|   |      | 6.2.2    | Multi-modal embeddings                            | 134 |

|   |      | 6.2.3    | Recent implementations of high-level planning for |     |

|   |      |          | mobile manipulation                               | 135 |

|   | 6.3  | Action   | Primitives for Mobile Manipulation                | 139 |

|   |      | 6.3.1    | Methods for creating primitives                   | 140 |

|   |      | 6.3.2    | Action primitive implementations                  | 141 |

|   | 6.4  | Identif  | fied Challenges                                   | 142 |

|   | 6.5  |          | ptual Architecture                                | 143 |

|   | 6.6  | Conclu   | usions and Outlook                                | 145 |

| 7 | An   | Overvi   | ew of the Automated Optical Inspection Edge AI    |     |

|   | Infe | rence S  | ystem Solutions                                   | 153 |

|   | Clai | idio Car | ntone and Alberto Faro                            |     |

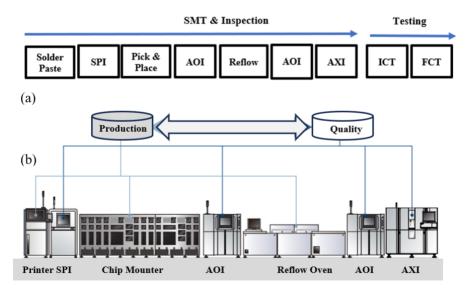

|   | 7.1  | Introd   | uction                                            | 154 |

|   | 7.2  | Overv    | iew of the Main Edge AI Solutions for AOI         | 155 |

|   | 7.3  | Comp     | aring EdgeAI solutions for AOI                    | 159 |

|   |      | 7.3.1    | Comparison using KPIs                             | 159 |

|   |      | 7.3.2    | Comparison using NFRs                             | 167 |

|   |      | 7.3.3    | Comparison using functional requirements          | 169 |

|    |       | 7.3.4 Advantages of ES with respect to the other            |     |

|----|-------|-------------------------------------------------------------|-----|

|    |       | approaches                                                  | 169 |

|    | 7.4   | Edge AI Solutions Demonstrator                              | 170 |

|    | 7.5   | Conclusion                                                  | 171 |

| 8  |       | cient AI-based Attack Detection Methods for Sensitive       |     |

|    | _     | e Devices and Systems                                       | 177 |

|    |       | iel Hirsch, Falk Hoffmann, Andrija Neskovic,                |     |

|    |       | ne Thermann, Rainer Buchty, Mladen Berekovic,               |     |

|    |       | Saleh Mulhem                                                |     |

|    | 8.1   | Introduction and Background                                 | 178 |

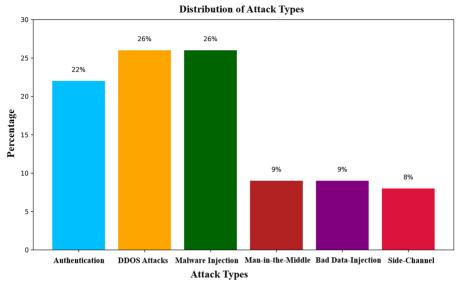

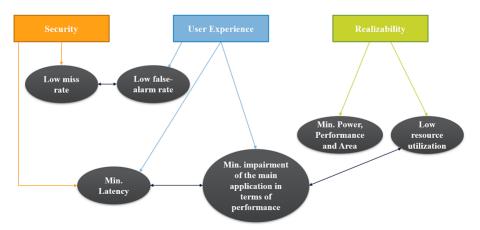

|    | 8.2   | Efficient Attack Detection                                  | 183 |

|    |       | 8.2.1 Requirements                                          | 183 |

|    |       | 8.2.2 Underlying Dataset                                    | 185 |

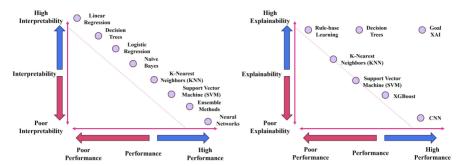

|    |       | 8.2.3 State-of- the-Art Attack Detection Methods            | 185 |

|    |       | 8.2.4 Selection of Applicable Algorithms                    | 188 |

|    | 8.3   | Discussion and Conclusion                                   | 189 |

| 9  | Exp   | lainability and Interpretability Concepts for Edge AI       |     |

|    | Syst  | ems                                                         | 197 |

|    | Ovid  | liu Vermesan, Vincenzo Piuri, Fabio Scotti, Angelo Genovese | 2,  |

|    | Rugg  | gero Donida Labati, and Pasquale Coscia                     |     |

|    | 9.1   | Introduction                                                | 198 |

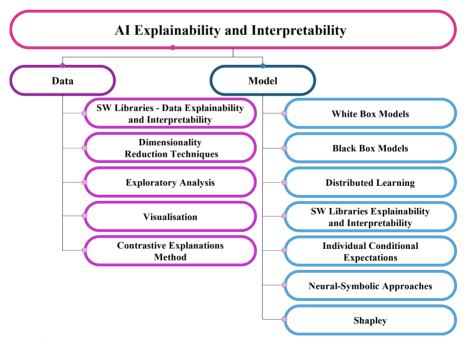

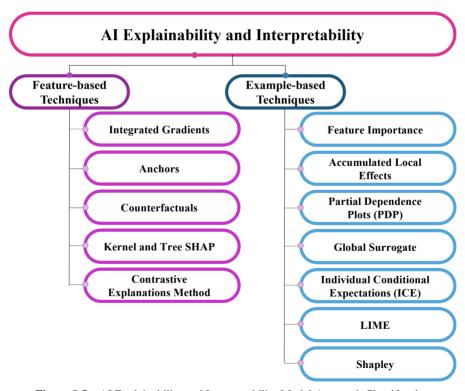

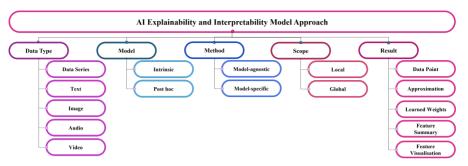

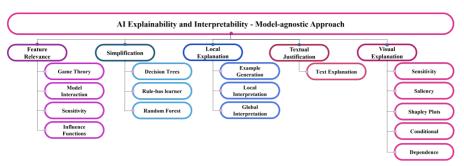

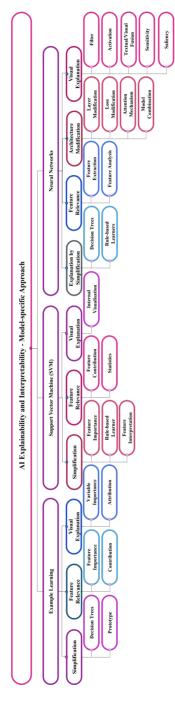

|    | 9.2   | AI Explainability and Interpretability Goals                | 202 |

|    | 9.3   | AI Explainability and Interpretability Methods              |     |

|    |       | and Techniques                                              | 204 |

|    | 9.4   | Benchmarking                                                | 211 |

|    | 9.5   | Edge AI Explainability and Interpretability                 | 213 |

|    | 9.6   | Challenges and Open Issues                                  | 214 |

|    | 9.7   | Conclusion                                                  | 216 |

| In | dex   |                                                             | 229 |

| Δŀ | out t | he Editors                                                  | 231 |

## **Preface**

## Taking the Next Steps on the Journey to Intelligent Pervasive Networked Systems

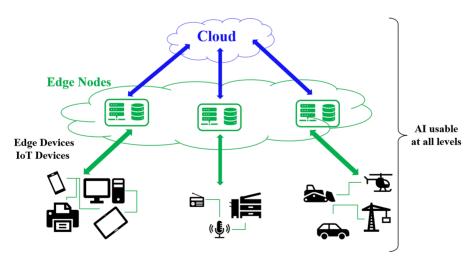

Given AI's astounding progress over the past few years, it is time to posit the next question: *How do we integrate AI into IoT devices at the edge of the network?*

The pre-question should, of course, be *why?* That is easy to answer: AIs are becoming pervasive, but conveying the data they need over networks is time-consuming, expensive, and potentially risky. Migrating them to the network edge mitigates those issues.

Edge AI marks a shift from traditional cloud-centric AI models to decentralised computing power embedded directly into edge devices.

Modern high-performance, low-power silicon makes the proposition to move these AIs into the devices themselves viable, even though we don't really have too much clarity yet on how that will be done, how the devices will be managed, or what the consequences for our networked systems architectures will be. In this book, we start the process of addressing those uncertainties.

In the following chapters, we start documenting the journey to address these questions, starting with considering the underpinnings of our current network technology in Chapter 1 before regarding how we can manage the lifecycle of AIs in IoT devices in Chapter 2. Chapters 3, 4 and 5 investigate how we might teach these AIs before Chapter 6 introduces how we might communicate with them (we can consider screens and keyboards depreciated in this brave new world). Chapters 7 and 8 present two example environments where such AIs will find application, and Chapter 9 addresses how they can explain their actions.

We don't have the answers to the big questions yet. If we did, we'd be off-creating VC-backed startups somewhere rather than coordinating research programs, but we know that we're at the start of the next chapter of a fascinating journey.

### xiv Preface

This book provides valuable insight to researchers working with edge AI technologies, machine and deep learning engineers, IoT designers, and intelligent systems developers looking to deploy intelligent solutions at the edge.

# **List of Figures**

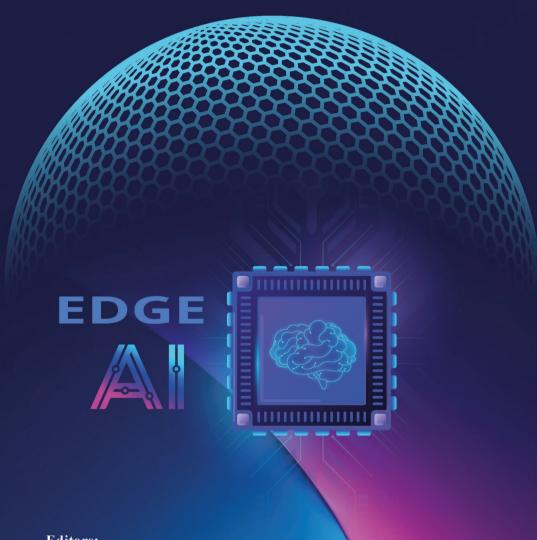

| Figure 1.1 | Network Topologies                                      | 2   |

|------------|---------------------------------------------------------|-----|

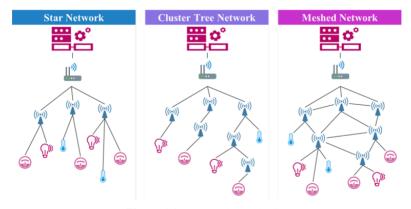

| Figure 1.2 | BLE Mesh Layered Architecture                           | 14  |

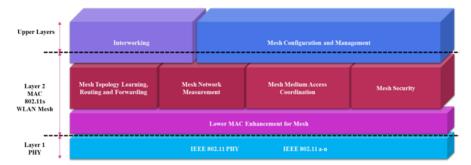

| Figure 1.3 | Wi-Fi Mesh Layered Architecture                         | 17  |

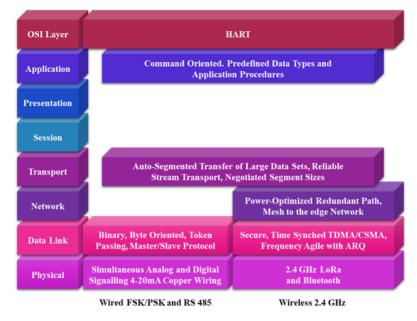

| Figure 1.4 | WirelessHART Protocol Architecture                      | 19  |

| Figure 1.5 | WirelessHART Mesh Networking                            | 20  |

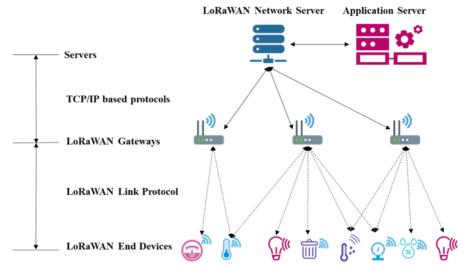

| Figure 1.6 | LoRaWAN Network Architecture                            | 25  |

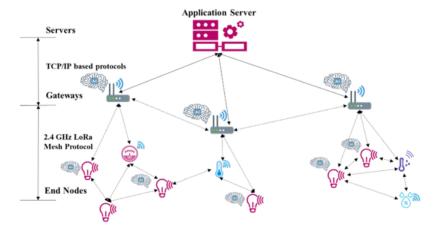

| Figure 1.7 | Edge AI Enabled LoRa Mesh Network                       | 27  |

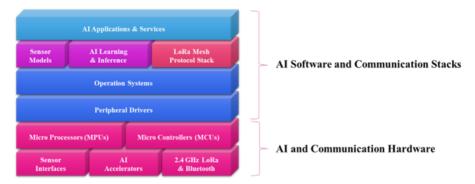

| Figure 1.8 | Conceptual Edge AI and LoRa Mesh Device Archi-          |     |

|            | tecture                                                 | 29  |

| Figure 2.1 | AI Lifecycle Stages Overview                            | 46  |

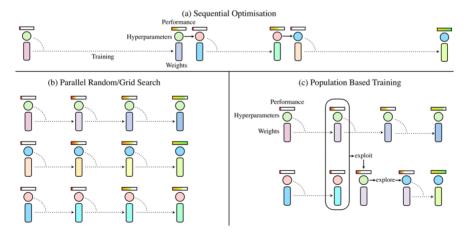

| Figure 2.2 | Overview of hyper-parameter training methodolo-         |     |

|            | gies [10] illustrating (a) sequential optimisation; (b) |     |

|            | parallel optimisation; (c) adaptive optimisation        | 51  |

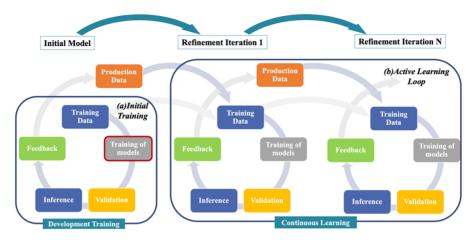

| Figure 2.3 | Model Training Overview illustrating (a) training       |     |

| J          | during the development stage and (b) training dur-      |     |

|            | ing the production stage                                | 59  |

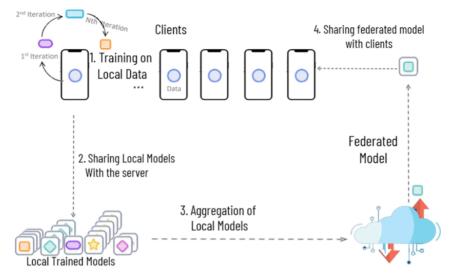

| Figure 3.1 | Client device sends their locally trained model         |     |

|            | updates to server for training the federated model      | 68  |

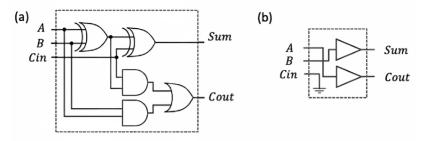

| Figure 3.2 | Logic diagram of (a) exact Full Adder, (b) Approx-      |     |

| J          | imate full adder                                        | 81  |

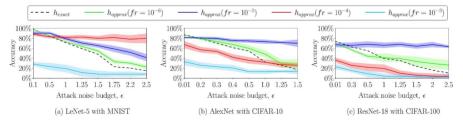

| Figure 3.3 | Precise and approximate models robustness under         |     |

| J          | PGD attack                                              | 81  |

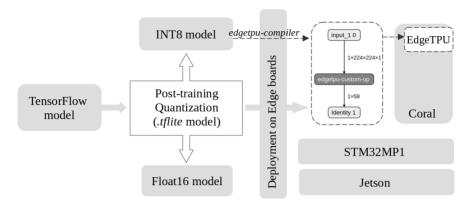

| Figure 4.1 | Workflow to Create a Tflite Model (Int8 And             |     |

| J          | Binary16) for Inference on Edge Boards: Google          |     |

|            | Coral Including the Compiled Model for the              |     |

|            | EdgeTPU, STM32MP1 and Jetson                            | 94  |

| Figure 4.2 | Coral Performance and Power Measurements                | 95  |

| Figure 4.3 | MP1 Performance and Power Measurements                  | 96  |

| Figure 4.4 | Jetson Performance and Power Measurements               | 96  |

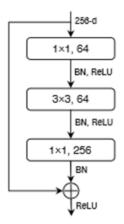

| Figure 5.1 | ResNet architecture [11]                                | 109 |

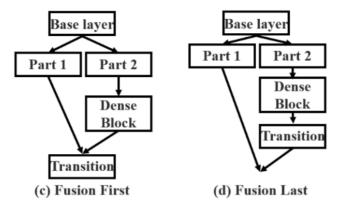

| Figure 5.2 | CSPNet (Identity Block - DenseNet)                      | 111 |

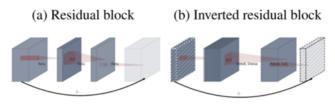

| Figure 5.3 | MobileNetv2 block                                   | 112 |

|------------|-----------------------------------------------------|-----|

| Figure 5.4 | MobileViT block [37]                                | 116 |

| Figure 5.5 | ConvNeXt Block [11]                                 | 119 |

| Figure 5.6 | EfficientNet Scaling [12]                           | 122 |

| Figure 6.1 | Proposed Mobile Manipulator Control System          | 144 |

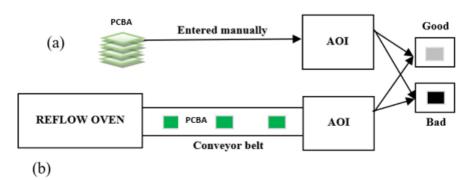

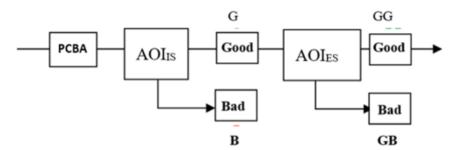

| Figure 7.1 | a) Printed Circuit Board (PCB) Assembly Process,    |     |

| C          | and b) Typical Implementation of the SMT Pro-       |     |

|            | duction Line, where production data are taken from  |     |

|            | Printer, Chip Mounter and Reflow, whereas quality   |     |

|            | data are taken from SPI, AOI and AXI                | 155 |

| Figure 7.2 | Main Inspection Machine Configurations for AOI in   |     |

| J          | the Digital Industry                                | 156 |

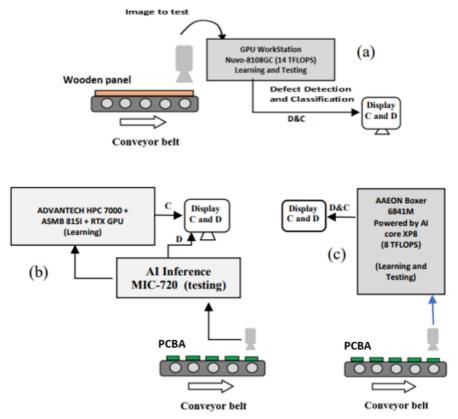

| Figure 7.3 | Edge AI AOI solutions from Neousys (a), Advan-      |     |

| C          | tech (b), and AAEON (c) for Defect Detection (D)    |     |

|            | and Classification (C). The model is Pre-trained on |     |

|            | the Workstation                                     | 158 |

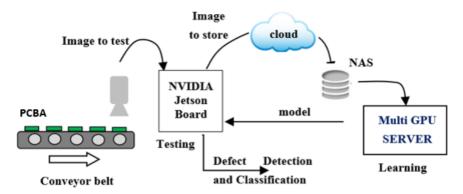

| Figure 7.4 | AOI Solution Consisting of an Edge Board for        |     |

|            | Testing and a GPU Server for Learning               | 159 |

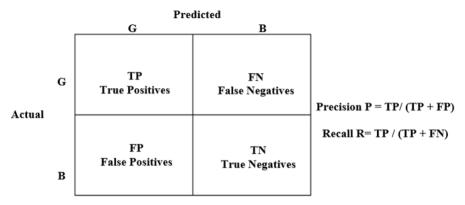

| Figure 7.5 | Confusion Matrix and Precision/Recall Formulas .    | 160 |

| Figure 7.6 | Repeating the AOI Check                             | 164 |

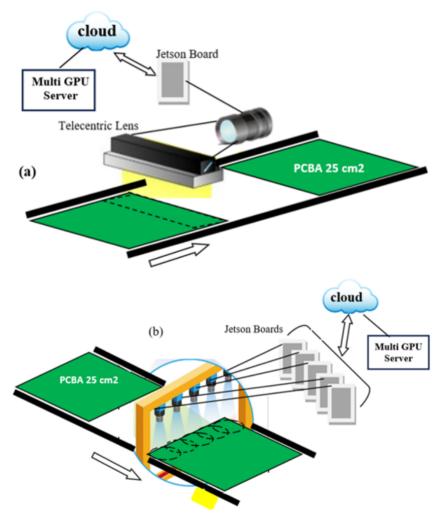

| Figure 7.7 | a) A Camera Equipped with a Testing Board Which     |     |

|            | Sends the Image of a PCB Slice of about 5 X 25      |     |

|            | cm Using a Telecentric Lens to a Testing Board,     |     |

|            | b) A Set of Five Cameras Equipped with Testing      |     |

|            | Boards. Images Are Sent to a Server to Update the   |     |

|            | Pre-Trained Model. The Server Periodically Sends    |     |

|            | the Updated Model to the Edge Testing Boards        | 167 |

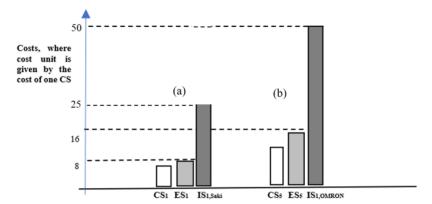

| Figure 7.8 | An Approximate Comparison of the Purchase Costs     |     |

|            | of CSs and ESs Equipped with one Camera Versus      |     |

|            | the Low Cost 2D Saki AOI (a), and the Purchase      |     |

|            | Costs of CSs and ES Equipped with Five Cam-         |     |

|            | eras Seats Versus the Professional 2D/3D OMRON      |     |

| <b>T</b>   | AOI (b)                                             | 168 |

| Figure 8.1 | Architecture of Edge System                         | 178 |

| Figure 8.2 | Possible Attacks against Edge Devices (Adapted      | 100 |

| <b>71</b>  | From [4])                                           | 180 |

| Figure 8.3 | Correlation of requirements                         | 183 |

|             | List of Figures                                     | XV11 |

|-------------|-----------------------------------------------------|------|

|             |                                                     |      |

| Figure 9.1  | AI Interpretability and Explainability vs Perfor-   |      |

| <u> </u>    | mance for Common ML Algorithms (Adapted             |      |

|             | from [7])                                           | 199  |

| Figure 9.2  | Conceptual Workflow explainable and interpretable   |      |

| 1 1guit >.2 | ML model development                                | 199  |

| T1 0.0      | -                                                   |      |

| Figure 9.3  | Responsibilities Across the AI Value Chain          | 201  |

| Figure 9.4  | Data and Model AI Explainability and Interpretabil- |      |

|             | ity Classification                                  | 205  |

| Figure 9.5  | AI Explainability and Interpretability Model        |      |

|             | Approach Classification                             | 206  |

| Figure 9.6  | AI Explainability and Interpretability Model-       |      |

| _           | Agnostic Approach Classification                    | 207  |

| Figure 9.7  | AI Explainability and Interpretability Model-       |      |

|             | Specific Approach Classification                    | 208  |

| Figure 9.8  | Feature- and Example-based AI Explainability and    |      |

|             | Interpretability Techniques                         | 210  |

# **List of Tables**

| Table 1.1                  | Frequency Band Overview                                 | 24  |

|----------------------------|---------------------------------------------------------|-----|

| Table 1.2                  | Frequency Band Overview                                 | 26  |

| Table 2.1                  | Types of Learning and corresponding tasks               | 47  |

| Table 2.2                  | Techniques to combat overfitting                        | 54  |

| <b>Table 2.2 Table 2.3</b> |                                                         | 55  |

|                            | Compression Techniques                                  | 33  |

| Table 2.4                  | Types of Automation based on the definition by SAE      | 60  |

|                            | International [21]                                      | 60  |

| <b>Table 4.1</b>           | Neural Network Description                              | 91  |

| <b>Table 4.2</b>           | Inference Accuracy Of The Quantized Model Before        |     |

|                            | (QAT) and After (PTQ) Training                          | 93  |

| <b>Table 4.3</b>           | Inference Performance and Latency Measurements for      |     |

|                            | Randomly Selected Images. Experiments Done on           |     |

|                            | x86 Standalone Server, Google Coral, STM32P1 and        |     |

|                            | NVIDIA Jetson Boards                                    | 95  |

| Table 4.4                  | QKeras quantization for different precisions            | 98  |

| <b>Table 4.5</b>           | FPGA performance and resource utilization               | 100 |

| <b>Table 4.6</b>           | Model perpormance on FPGA                               | 100 |

| Table 5.1                  | CNNs based model optimization since AlexNet             | 112 |

| Table 5.2                  | MCUNet memory optimization compared to MobileNet        |     |

|                            | and MobileNetv2                                         | 114 |

| Table 5.3                  | CNNs based model optimization since AlexNet             | 115 |

| Table 5.4                  | Optimized transformers and hybrid transformers per-     | 110 |

| 1abic 5.4                  | formance by scale                                       | 118 |

| Table <i>5.5</i>           |                                                         | 110 |

| Table 5.5                  | ConvNeXt compared to hybrid transformers perfor-        | 120 |

|                            | mance by scale.                                         | 120 |

| Table 5.6                  | Efficient neural network architectures with neural net- |     |

|                            | work soorah                                             | 122 |

# **List of Contributors**

Adrien, Prost-Boucle, Institute of Engineering Univ. Grenoble Alpes, France

Alberto, Faro, Deepsensing, DEEPS, Italy

Ana, Pinzari, Institute of Engineering Univ. Grenoble Alpes, France

Andrija, Neskovic, Universität zu Lübeck, Germany

Angelo, Genovese, Università degli Studi di Milano, Italy

Celine, Thermann, Universität zu Lübeck, Germany

Christelle, Rabache, Institute of Engineering Univ. Grenoble Alpes, France

Claudio, Cantone, High Technology Systems H.T.S. srl, Italy

Claus, Lenz, Cognition Factory GmbH, Germany

Cordula, Conrady, IMST GmbH, Germany

**Daniel, Hirsch**, NXP Semiconductors, Germany

**Dinu, Purice**, Cognition Factory GmbH, Germany

Elhadj, Doguech, Université Polytechnique Hauts-De-France, France

Fabio, Scotti, Università degli Studi di Milano, Italy

Falk, Hoffmann, NXP Semiconductors, Germany

Francesco, Barchi, Universita di Bologna, Italy

Frédéric, Pétrot, Institute of Engineering Univ. Grenoble Alpes, France

Gatis, Gaigals, Institute of Electronics and Computer Science, Latvia

Hans-Erik, Sand, NXTECH AS, Norway

Ihsen, Alouani, Université Polytechnique Hauts-De-France, France

Iyad, Dayoub, Université Polytechnique Hauts-De-France, France

Janis, Arents, Institute of Electronics and Computer Science, Latvia

#### xxii List of Contributors

Janis, Judvaitis, Institute of Electronics and Computer Science, Latvia

Kai, vorm Walde, IMST GmbH, Germany

Lilian, Hollard, Université de Reims Champagne-Ardenne, France

Lucas, Mohimont, Université de Reims Champagne-Ardenne, France

Luiz, Angelo Steffenel, Université de Reims Champagne-Ardenne, France

Marcello, Coppola, STMicroelectronics, France

Mladen, Berekovic, Universität zu Lübeck, Germany

Modris, Greitans, Institute of Electronics and Computer Science, Latvia

Oskars, Vismanis, Institute of Electronics and Computer Science, Latvia

**Ovidiu, Vermesan**, SINTEF AS, Norway

Pasquale, Coscia, Università degli Studi di Milano, Italy

Peteris, Racinskis, Institute of Electronics and Computer Science, Latvia

Rainer, Buchty, Universität zu Lübeck, Germany

Roy, Bahr, SINTEF AS, Norway

Ruggero, Donida Labati, Università degli Studi di Milano, Italy

Saleh, Mulhem, Universität zu Lübeck, Germany

Taha, Yassine Abidi, Université Polytechnique Hauts-De-France, France

**Thorsten, Röder**, Cognition Factory GmbH, Germany

**Toms, Eduards Zinars**, Institute of Electronics and Computer Science, Latvia

**Tore, Karlsen**, *ProLux AS*, *Norway*

Vincenzo, Piuri, Università degli Studi di Milano, Italy

# **List of Abbreviations**

AC Approximate Computing

AES Advanced encryption standard AIA Artificial intelligence act

AI Artificial intelligence

AOI Automated Optical Inspection

AODV Ad hoc on-demand distance vector

ASIC Application-specific integrated circuit

B.A.T.M.A.N. Better approach to mobile ad-hoc networking

(protocol)

BLE Bluetooth low energy

BW Bandwidth

CMM Coordinate mount metrology

CNN Convolutional neural network

CPU Central processing unit

CS AOI Solution using cloud server receiving

images from cameras for both learning and

testing

CSS Chirp spread spectrum DAG Directed acyclic graph

DL Deep learning

DLG Deep leakage from gradients

DNN Deep neural network

DnC Divide and conquer

DSR Dynamic source routing

ES AOI Solution using testing boards at the edge

and cloud server receiving images from cameras

for learning

FAN Field area network FCT Functional test

FEC Forward error correction

FL Federated learning

#### xxiv List of Abbreviations

FPGA Field programmable gate array

GAM Generalised additive models

GDPR General data protection regulation

GPU Graphical processing unit

GS AOI Solution using GPU workstation receiving

images from cameras for both learning and

testing

GSA Global sensitivity analysis

IoT Internet of Things

ICT In circuit test

IR Intermediate representation

IS AOI Solution using inspecting machine close to

the conveyor belt

JIT Just in time compilation

Lime Local interpretable model-agnostic explanation

LLN Low-power and lossy network LoRaWAN Long-range wide area network

LUT LookUp table

M2M Machine-to-machine

MAC Multiply accumulate; Medium/media access

control layer

MANET Mobile ad-hoc network

MAPLE Model agnostic supervised local explanation

MEMS Micro-electromechanical system

ML Machine learning

MLE Mesh link establishment

MLP Multi-layer perceptron

MPR Multi-point relay

MRI Magnetic resonance imaging NLP Natural language processing

OGM Originator message

OLSR Optimised link state routing

PCBA Printed circuit board assembly, sometimes

printed circuit board assembler

PDP Partial dependence plot

PTQ Post-training quantization

QAT Quantization aware training

OTA Over-the-air PHY Physical layer QoS Quality of service

RNN Recursive neural network

RPL Routing protocol for low-power and lossy

networks

SDLC Software development lifecycle

SHAP Shapley additive explanation

SIMD Single instruction multiple data

SMT. Surface mount technology.

SMT Surface mount technology

SoC System on a chip

SPI Solder paste inspection TPU Tensor processing unit

TTL Time to live

TVM Tensor virtual machine

WLAN Wireless local area network

WMN Wireless mesh network

WSN Wireless sensor network

XAI Explainable AI

XLA Accelerated linear algebra

YOLO You only look once - Object detection model

known for its speed and accuracy.

# **Edge AI LoRa Mesh Technologies**

Ovidiu Vermesan<sup>1</sup>, Kai vorm Walde<sup>2</sup>, Roy Bahr<sup>1</sup>, Cordula Conrady<sup>2</sup>, Janis Judvaitis<sup>3</sup>, Gatis Gaigals<sup>3</sup>, Tore Karlsen<sup>4</sup>, Marcello Coppola<sup>5</sup>, and Hans-Erik Sand<sup>6</sup>

#### **Abstract**

Intelligent connectivity at the edge combines wireless communication, edge artificial intelligence (AI), edge computing and internet of things (IoT) technologies to perform machine learning (ML) and deep learning (DL) on connected edge devices. Low latency, ultra-low-energy intelligent IoT devices with on-board computing, and a distributed architecture and analytics are essential to drive intelligent connectivity.

Intelligent wireless mesh technologies exploit multiple interconnected devices, or nodes, to create a distributed network integrated with edge AI analytics using ML and DL algorithms. In an intelligent wireless mesh network (WMN), each node has embedded intelligence and can communicate directly with its neighbouring nodes and transfer data efficiently to other nodes. Compared with traditional point-to-point wireless networks, the intelligent wireless mesh approach offers several advantages, including increased coverage, redundancy, scalability and resilience.

The convergence of multiple technologies (connectivity, edge AI, IoT, distributed architectures and federated learning) delivers intelligent edge

<sup>&</sup>lt;sup>1</sup>SINTEF AS, Norway

<sup>&</sup>lt;sup>2</sup>IMST GmbH, Germany

<sup>&</sup>lt;sup>3</sup>Institute of Electronics and Computer Science, Latvia

<sup>&</sup>lt;sup>4</sup>ProLux AS, Norway

<sup>&</sup>lt;sup>5</sup>STMicroelectronics, France

<sup>&</sup>lt;sup>6</sup>NXTECH AS, Norway

mesh communication systems that perform efficient connectivity by optimising data rates, coverage, energy, and interference.

This article overviews the latest advancements in edge AI long-range mesh technologies and applications, highlights state-of-the-art mesh communication requirements and implementations and identifies future research challenges and directions.

**Keywords:** mesh communication technologies, edge artificial intelligence, LoRaWAN, LoRa mesh.

#### 1.1 Introduction

Star, tree and mesh networks are examples of topologies used in communication networks. Each is suitable for different application scenarios. An illustration of the different network architectures is shown in Figure 1.1.

Star networks are simple to set up and manage because they have centralised control points. However, this makes them more susceptible to single-point failures. Mesh networks offer high redundancy and self-healing (e.g., recovery from a link failure), making them more reliable and fault tolerant at the cost of increased complexity.

Wireless mesh technologies play an essential role in creating robust and flexible wireless networks that address modern connectivity challenges.

In a star topology, all nodes are directly connected to a single central root node, often referred to as a hub. Direct peer-to-peer communication is not supported; all nodes must communicate through this central hub.

Figure 1.1 Network Topologies

Networks with cluster-tree topologies are divided into so-called clusters. Each cluster consists of a group of nodes connected to a local central node referred to as the cluster head. The cluster head coordinates the communication within its cluster. The tree terminology refers to the cluster heads which are organised in such a hierarchical structure. Communication from node to node may involve routing via multiple cluster heads.

Wireless mesh technologies use multiple interconnected nodes which can communicate directly with their neighbours nodes. This approach offers several advantages, including increased coverage, redundancy, resilience, and scalability.

Mesh communication technologies use distributed networking methods that typically create a decentralised and self-configuring network. Each node can also act as a repeater to extend network coverage and improve resilience.

The convergence of edge computing, edge AI, federated learning and IoT can create multi-dimensional architectures consisting of a wide range of heterogeneous entities with different sensing/actuating, connectivity, processing, and intelligence capabilities connected with applications in a dynamic mesh network linked by platforms and distributed services located at the edge level. Some of the technologies contributing to enhancing the capabilities of intelligent mesh connectivity include:

Edge AI - The deployment of AI algorithms and data processing capabilities directly on edge devices, rather than relying on centralised cloud servers, brings the following benefits:

- Real-time decision making By processing data locally, AI models can make fast decisions without the latency of sending data to remote servers, enabling rapid responses to critical events.

- Data privacy and security Edge AI reduces the need to transmit sensitive data to the cloud, increasing privacy and decreasing the consequence of data breaches.

- Bandwidth efficiency Edge AI can filter and prioritise data before transmission, reducing bandwidth demands.

Federated Learning (also called collaborative learning) is a machine learning method in which edge devices collaboratively contribute to a global model while keeping their data locally. Federated learning can play a significant role in enhancing the combination of edge AI, IoT and communication technologies.

*Privacy preservation*: Federated learning avoids the transmission of raw data to a central server. This ensures that sensitive data remain on the edge devices, addressing privacy concerns and complying with data protection regulations.

Bandwidth efficiency: By training models locally on edge devices, federated learning reduces the need to send large amounts of data to the cloud for model training. This optimises bandwidth usage, making it more efficient for IoT devices with limited communication capabilities, such as long-range (LoRa)-based communication devices. LoRa is a wireless spread spectrum modulation technique derived from the chirp spread spectrum (CSS), which enables long-range communication between devices with low power consumption. The technology was initially developed by a company called Cycleo SAS and later acquired by Semtech Corporation [1], a semiconductor company specialising in analogue and mixed signal circuits.

*Improved model performance*: Federated learning allows IoT devices to continuously improve their local models. This can result in better model performance and adaptability over time, as each device benefits from the collective intelligence of the entire network.

*Decentralised intelligence*: Federated learning distributes intelligence across edge devices, promoting decentralised data processing and decision-making. This leads to increased resilience in the overall system.

Collaboration and knowledge sharing: By collaborating on model training, edge devices share knowledge and insight. This collaborative approach fosters rich and diverse learning experiences.

*Reducing infrastructure costs*: Federated learning reduces the need for large-scale cloud infrastructure for centralised model training. This results in cost savings in respect of data transmission and cloud computing resources.

*Versatility and scalability*: Federated learning can be adapted to many different edge devices and network architectures. It can scale efficiently making it suitable for IoT networks with diverse deployments and configurations.

Federated learning complements the combination of edge AI, IoT and LoRa by enhancing privacy, efficiency, model performance and collaboration. It empowers IoT networks with intelligent decision-making capabilities while respecting data privacy and promoting decentralised data processing.

**Internet of Things (IoT)** is related to the network of interconnected devices and sensors that collect, exchange, and analyse data. By integrating IoT with edge AI and LoRa technology, it becomes a powerful enabler across various domains:

- Remote monitoring and control IoT sensors can collect data from different environments, enabling remote monitoring and control of processes, infrastructure, and assets.

- Predictive maintenance IoT data, when combined with edge AI analytics, allows the prediction of equipment failures, optimisation of maintenance schedules and reductions in downtime.

- Energy management IoT deployments combined with edge AI enable efficient energy management, waste reduction and improved urban services in smart city applications.

The combination of edge AI and mesh communication has several benefits, especially when infrastructure is impracticable or unavailable. Mesh networks enable flexible, reliable, and scalable networks. They are increasingly used in industrial IoT, energy, smart homes, agri-food and beverage, disaster recovery operations and smart city applications.

This chapter is organised into the following sections. Section 1 introduces the research area and the state of play of technology development. Sections 2 and 3 provide an overview of the state of the art of existing wireless mesh technologies and their primary functions, operating characteristics and actual advantages and disadvantages. Section 4 describes the LoRa wireless modulation technique and the long-range wide area network (LoRaWAN) technology, the main architectures, the architectural building blocks, and their characteristics. Section 5 covers enabling technologies (e.g., edge AI, edge computing, internet of intelligent things, artificial intelligence of things) and integration with LoRa mesh to enhance and optimise communication performance and mesh-based systems' collaborative and cooperative capabilities. Section 6 presents potential applications for LoRa mesh connectivity, edge AI and IoT systems and emphasises the requirements for intelligent communication and convergence with other technologies. Section 7 outlines the conceptual edge AI LoRa mesh device architecture. Section 8 analyses the state of play and future research directions and highlights several challenging open issues for intelligent edge LoRa meshes. Finally, Section 9 summarises the main points for discussion.

# 1.2 Overview of the State-of-the-Art Wireless Mesh **Technologies**

Meshes are networks that create a decentralised and robust structure where each node can communicate directly with neighbouring nodes.

Nodes are interconnected and, depending on the network topology, there can be multiple connection pathways for each node. Connections between nodes may be dynamically updated and optimised through a built-in mesh routing table. As nodes enter and exit the network, the mesh topology enables the nodes to reconfigure routing paths based on the new network configuration.

Mesh topology and ad-hoc routing assures stability in the face of changing communication conditions or node failure.

Mesh networks use a distributed approach, where each node can act as a repeater to extend network coverage and improve resilience. The critical characteristics of mesh communication technologies include:

- Decentralisation mesh networks are not dependent on a single central

point of control. Each node can communicate with its neighbour, allowing messages to bounce from one node to another until they reach their

destination.

- **Self-configuration** mesh networks are capable of self-organisation. When nodes are added or removed the network can dynamically reconfigure itself to accommodate these changes.

- **Redundancy and reliability** due to their decentralised nature and self configuration capability, mesh network topologies are more resilient to node failure or network disruption.

- Extended coverage mesh networks can cover an extended area by using multiple nodes as relays. This provides an advantage in cases when establishing a traditional infrastructure might be challenging or costly.

- **Ad-Hoc networking** mesh communication technologies enable adhoc networking, where devices can spontaneously create a network without relying on pre-existing infrastructure.

- Geographical scalability mesh networks can quickly expand their coverage by adding more nodes which do not need to be in direct communication

## 1.2.1 Mesh components and roles

Wireless mesh networks usually consist of routers, nodes, and coordinators as described below:

• **Routers** – these devices form the backbone of a wireless mesh network. They are typically more powerful than simple nodes with enhanced processing capabilities and are responsible for routing data within the

whole network. Mesh routers communicate with other routers and nodes in the network to forward data packets along the most efficient path to reach their intended destination.

- Nodes these are individual devices connected to the mesh network. They can be computers, smartphones, sensors, IoT devices, or any other device capable of wireless communication. Mesh nodes are typically senders, receivers, or relay points. Unlike traditional networks, mesh nodes in a wireless mesh network can communicate directly with each other, creating multiple data transmission paths. This decentralised communication architecture enhances the network's reliability and overall performance.

- Coordinators mesh coordinators are nodes with specialised roles in some wireless mesh network protocols. They act as central control points for the entire mesh network. A coordinator is responsible for managing and organising the network, assigning roles to other nodes (such as routers or end devices), and controlling aspects of the network's operation. They handle tasks like channel allocation, network formation, and security management. In some mesh network implementations, coordinators have a critical role in preserving the network's stability and performance. On one hand, central coordinators can offer efficient control and coordination; on the other hand, they can also become a single point of failure, potentially disrupting the entire network and compromising one of the key advantages of mesh topologies.

- Decentralised functionality this approach eliminates the central mesh coordinator. Instead, the process of decision-making and control is distributed across multiple nodes. Nodes may possess a degree of autonomy, enabling them to make local decisions based on independent observations and interactions with neighbouring nodes. Local decisions collectively contribute to the overall behaviour of the network.

## 1.2.2 Wireless routing concepts

One of the key elements for wireless mesh communication, routing protocols are designed to enable communication and data exchange between devices in a wireless network. These protocols establish routes for data transmission and determine the best paths for information to flow from a source to a destination. The functions of a wireless routing protocol vary depending on the specific protocol used and the type of wireless network. We present a

general overview of the common functionalities of these wireless routing protocols:

- **Neighbour discovery** in wireless networks, devices must discover neighbours to establish direct communication links.

- Route discovery when a device wishes to send data to another device, a route discovery process is initiated. During the process, the device searches direct links or for potential intermediate devices (routers) that can relay the data towards the destination. This process can involve broadcasting or multicasting route request packets to nearby devices to find potential routes.

- Route maintenance once a route is established, the routing protocol is responsible for maintaining the health and stability of it. This includes monitoring the status of the intermediate devices along the path and detecting any changes, such as link failures or device mobility. If a route becomes unavailable, the routing protocol triggers a route repair process to find an alternative path.

- Routing metrics wireless routing protocols use various metrics to determine the quality and efficiency of potential routes. Metrics include signal strength, link quality, distance, and available bandwidth. The routing protocol uses these metrics to select the preferred routes based on network conditions and requirements. The current battery state of a node may also be a metric to implement a kind of energy-balancing policy.

- **Data forwarding** once a route is established, the data packets are forwarded from one router to the next until they reach their destination. Each router in the path makes a forwarding decision based on the routing table and the packet's destination address.

- Adaptation to network changes wireless routing protocols are constructed to adapt to changes in the network topology, such as device mobility, link quality fluctuations, or node failures. They continuously monitor the network and adjust the routing paths to ensure reliable and efficient data transmission.

## 1.3 Routing protocols

Some standard wireless routing protocols, include Optimised Link State Routing (OLSR) [29][30][31][33], Ad hoc On-Demand Distance Vector

(AODV) [34][35], Dynamic Source Routing (DSR) [36][37] and Routing Protocol for Low-Power and Lossy Networks (RPL) [38][39][40]. Each protocol has specific features, advantages, with use cases tailored for different wireless networks and applications. There follow some details about the algorithms and their pros and cons.

#### 1.3.1 Ad hoc on-demand distance vector (AODV)

AODV is a demand-driven reactive wireless routing protocol that establishes routes only when needed. When a source node requests to send data to a destination node, it initiates a route discovery process to find the most efficient path. The protocol uses sequence numbers to ensure loop-free routes and maintains a routing table to store information about discovered routes.

Pros:

- Reduced overhead AODV minimises control message overhead by initiating route discovery only when necessary. This helps conserve network resources and reduces unnecessary traffic.

- Loop-free routes using sequence numbers ensures that routes are loop-free, improving route stability and reliability.

- Proactive link failure detection AODV employs proactive link failure detection to quickly identify failed links and initiate route repair, ensuring data continues to flow via alternative paths.

- Scalability AODV performs well in moderately sized networks and maintains route information for frequently used paths, reducing route discovery latency.

#### Cons:

- High latency for new routes AODV's on-demand route discovery process can introduce delays in finding a new route, especially in large networks or sparse topologies.

- Route rediscovery several cases (link changes, node mobility, malicious nodes, battery depletion, network congestion or topology changes) lead to frequent route rediscovery, increasing control message overhead.

- **Suboptimal routes** sometimes, AODV may not find the shortest path in specific network scenarios, leading to less efficient data transmission.

AODV balances control message overhead and route discovery latency, making it suitable for dynamic networks with changing topologies. However, its performance may vary depending on network size, mobility patterns, and the frequency of route changes.

# 1.3.2 Optimized link state routing (OLSR)

OLSR is a proactive routing protocol that uses a hybrid approach, combining both proactive and reactive mechanisms. It optimises link-state information exchange to minimise overhead while ensuring efficient route computation and maintenance. OLSR uses Multi-Point Relays (MPRs) to reduce control message flooding and speed up route discovery.

#### Pros:

- Reduced control message overhead OLSR uses MPRs to limit the number of nodes participating in control message dissemination. This decreases control overhead and improves scalability, making it suitable for large networks.

- Proactive and reactive hybrid approach OLSR combines proactive link-state information with reactive route discovery. It provides real-time responsiveness while minimising the amount of control traffic generated.

- Loop-free routes OLSR guarantees loop-free routes and enhances route stability and reliability.

- Fast route recovery MPRs and proactive topology updates enable quick route recovery and repair in case of link failures.

- Better convergence OLSR converges quickly and efficiently, enabling devices to find optimised routes with lower latency.

#### Cons:

- Memory and computation requirements OLSR requires storing and managing additional topology information due to MPRs. This imposes overhead which might be critical on devices with limited resources.

- Increased initial setup overhead the initial setup phase in OLSR involves the exchange of control messages to determine MPRs which leads to higher overhead during network initialisation.

- Relatively complex implementation compared to other protocols, the implementation and management of OLSR can be more complex due to its hybrid nature and the need to optimise MPR selection.

OLSR balances proactive and reactive mechanisms, making it suitable for dynamic networks with varying traffic patterns and topology changes. Its efficiency in controlling message overhead and quick route convergence makes it a viable choice for both small and large-scale wireless networks.

# 1.3.3 Dynamic source routing (DSR)

DSR is an on-demand routing protocol that establishes routes between nodes only when needed. When a source node requests to send data to a destination node, it initiates a route discovery process to find a path. The route discovery process is based on source routing, which includes the complete route in the data packet. Intermediate nodes use this route information to forward the packet to the next hop until it reaches the destination. Pros:

- Reduced overhead DSR minimises control message overhead since route discovery is initiated only when needed, conserving network resources and reducing unnecessary traffic.

- Loop-free routes DSR ensures loop-free routes through sequence numbers and route caching, enhancing route stability and reliability.

- Efficient source routing including the complete route in the data packet enables efficient source routing, eliminating the need for intermediate nodes to maintain routing tables.

- Route repair DSR supports quick route repair in case of link failure, as the source node can initiate a new route discovery process to find an alternative path.

#### Cons:

- Route discovery latency the route discovery process in DSR can introduce delays, especially in large networks or sparse topologies, as it requires time to find a route to a new destination.

- Increased packet overhead including the complete route in the data packet leads to larger packet sizes, especially for long routes, resulting in increased packet overhead.

- Route maintenance overhead frequent mobility or link changes can lead to higher route maintenance traffic, as DSR requires regular route updates to adapt to topology changes.

- Source routing overhead While source routing eliminates the need for routing tables in intermediate nodes, it increases the size of data packets, which can be a concern for resource-constrained devices.

DSR offers a simple and efficient approach to routing in Mobile Ad-hoc Networks (MANETs), particularly for networks with moderate mobility and communication demands. Its reactive nature allows it to adapt to changing network conditions, while the use of source routing eliminates the need for routing tables in intermediate nodes. The trade-offs include potential

overhead from route discovery and maintenance, which should be considered when selecting DSR as the routing protocol for specific MANET deployments.

# 1.3.4 Routing protocol for low-power and lossy networks (RPL)

RPL is a specialised routing protocol for low-power and lossy networks (LLNs) as commonly been in IoT and wireless sensor networks. RPL is a proactive routing protocol that forms a directed acyclic graph (DAG) to route data in LLNs efficiently. It organises devices into a tree-like structure, with a root node at the top. It optimises routes using objective functions based on specific metrics, such as energy efficiency or latency. RPL is tailored for devices with limited resources, making it well suited for battery-powered IoT devices that require reliable and energy-efficient communication. Pros:

- Energy efficiency RPL is designed to minimise energy consumption in resource-constrained devices. It optimises routes to ensure that energy is conserved during data transmission, thus prolonging the battery life of IoT devices and the entire IoT system.

- Adaptability to LLNs RPL's tree-like DAG structure is well-suited for LLNs, where devices may have limited processing power and intermittent connectivity.

- Objective function flexibility RPL allows network designers to choose different objective functions based on their specific requirements, such as energy efficiency, latency, or reliability.

- Self-configuring and self-healing RPL networks can self-configure and adapt to changes in network topology, including the addition or removal of devices. It also supports self-healing, where the network finds alternative routes if link failures occur.

#### Cons:

- Complex configuration configuring RPL for specific use cases can be complicated due to the various parameters and objective functions that must be considered. Proper tuning and optimisation may require expertise and considerable time.

- Scalability for large networks while RPL performs well in small to medium-sized LLNs, it may face challenges in large networks, where the tree-like structure can lead to increased control traffic and reduced scalability.

• Overhead in highly mobile networks - in highly mobile LLNs frequent changes in the network topology may result in increased control message overhead as the network adapts to mobility.

Overall, RPL's focus on energy efficiency and adaptability to low-power and lossy networks makes it a strong choice for IoT and wireless sensor networks. It effectively addresses the unique challenges posed by resourceconstrained devices, allowing them to form reliable and efficient communication links while optimising energy consumption. However, careful configuration and consideration of scalability in large networks are essential to ensure the protocol's effectiveness for specific deployment scenarios.

#### 1.3.5 Wireless mesh protocols

Mesh communication technologies offer flexible, reliable, and scalable networking solutions, and several protocols include mesh topologies. A short overview of mesh protocols such as B.A.T.M.A.N., Bluetooth Mesh, OpenThread, Thread, ZigBee, Wi-Fi, Wi-SUN, WirelessHART, Z-WAVE and 6LoWPAN is presented before focusing on the LoRa mesh protocol and applications.

#### 1.3.5.1 B.A.T.M.A.N

The protocol Better Approach To Mobile Ad-hoc Networking (B.A.T.M.A.N.) [11] is a multi-hop ad-hoc mesh network routing protocol where each node transmits broadcast or originator messages (OGMs) to notify neighbouring nodes about its presence. These neighbours re-broadcast the OGM.s based on specific rules to inform their neighbours about the presence of the original initiator. The network is steeped with OGM s that are small, with a typical raw packet size of 52 bytes, including IP and UDP overhead. OGMs contain at least the originator's address, the address of the transmitting packet's node, a Time to Live (TTL) and a sequence number.

The approach of the B.A.T.M.A.N. algorithm is to divide the knowledge about the best end-to-end paths between nodes in the mesh to all participating nodes.

B.A.T.M.A.N. uses a proactive routing approach, which means it continuously maintains up-to-date routing information without waiting for a specific request to transmit data. Instead of relying on global routing tables, each node perceives and retains only the information about the best next hop towards all other nodes. Thereby the condition for overall network knowledge about local topology changes is unnecessary. Since wireless mesh networks are subject to frequent changes, B.A.T.M.A.N. is designed to be adaptive and capable of quickly reconfiguring routes when nodes join, leave, or move within the network.

The protocol also supports load balancing by distributing traffic across multiple paths to prevent congestion and optimise the overall network performance.

# 1.3.5.2 Bluetooth Low Energy

Bluetooth Low Energy (BLE) [13] is optimised for low power consumption to address small-scale consumer IoT applications. BLE is integrated into several IoT devices, and data is conveniently communicated to and visualised on smartphones. The Bluetooth Mesh specification aims to enable a scalable deployment of BLE devices.

BLE provides versatile indoor localisation features, and IoT beacon networks are used for different IoT service applications. BLE is incompatible/non-interoperable with Bluetooth, and a dual-mode device is required to achieve interoperability.

BLE uses multiple techniques to ensure low power consumption implementing the data protocol to create low-duty-cycle transmissions, combined with very low-power sleep modes.

Bluetooth Low Energy Mesh [12] protocol is a networking technology built on the BLE standard. It enables large-scale, reliable, secure communication between many devices, forming a mesh network. This mesh network allows devices to communicate with each other and extend the range of the network.

A device can have one or more logical elements in the Bluetooth Mesh network. Each element represents a specific functionality or component of the device, and each element is assigned a unique address within the network.

Figure 1.2 BLE Mesh Layered Architecture

Bluetooth Mesh devices use models to define their behaviour and capabilities. Models represent how a device handles messages, what types of messages it supports, and how it behaves in the mesh.

Provisioning is the process of securely adding a new device to the mesh network. Encryption keys and other necessary information are exchanged between the new device and the network during this process.

# 1.3.5.3 OpenThread and Thread

Thread [14] is a mesh networking low-power wireless protocol based on Internet Protocol version 6 (IPv6), designed to address the interoperability, security, power, and architecture challenges of the IoT. Thread utilises 6LoWPAN that employs the IEEE 802.15.4 wireless protocol with mesh communication. Thread is IP-addressable, with cloud access and advanced encryption standard (AES).

Thread uses a mesh network topology in the 2.4 GHz frequency spectrum, providing data rates of 250 kbps with a coverage range of 30 m. Security uses a 128-bit AES encryption system and the encryption cannot be disabled.

Thread utilises a network-wide key for inscription that is applied at the Media Access Layer (MAC). The key is employed as specified in IEEE 802.15.4. Attacks on Thread network originating over-the-air from outside the network are protected by IEEE 802.15.4 security mechanisms. The Thread network's nodes exchange frame counters with their neighbours via a Mesh Link Establishment (MLE) handshake. The protection against replay attacks is done via frame counters. Thread lets the application use various internet security protocols for end-to-end communication and can connect up to 250 devices.

OpenThread, released by Google, is an open-source implementation of Thread that implements all Thread networking layers (IPv6, 6LoW-PAN, IEEE 802.15.4 with MAC security, Mesh Link Establishment, Mesh Routing), device roles, and Border Router support.

# 1.3.5.4 ZigBee

ZigBee [15] is a short-range, low-power, wireless standard deployed in a mesh topology to extend coverage by relaying IoT sensor data over multiple sensor nodes.

The Zigbee standard works on the IEEE 802.15.4 physical radio specification and runs in unlicensed bands such as 2.4 GHz, 915 and 868 MHz.

Zigbee 3.0 sustains wireless networks' increasing scale and complexity and deals with extensive local networks of over 250 nodes. The data rates provided are 250 kbps (2.4 GHz), 40kbps (915 MHz) and 20kbps (868 MHz). Zigbee also handles the dynamic behaviour of the networks (with nodes disappearing, appearing, and re-appearing in the network topology) and permits orphaned nodes, resulting from the loss of a parent to rejoin the Zigbee network through another parent.

The self-healing structure of state-of-the-art Zigbee Mesh networks permits nodes to drop out of the network without disrupting internal routing. Zigbee supports over-the-air (OTA) upgrades during device operation and provides enhanced network security by employing a coordinator/trust centre, which creates the network and oversees the allocation of network and link security keys to joining nodes or distributed security where there is no coordinator/trust centre. The Zigbee router node can provide the network key to joining nodes.

#### 1.3.5.5 Wi-Fi

Wi-Fi (IEEE/ISO/IEC 8802-11-2022) is a standard defining the characteristics of a wireless local area network (WLAN). The name Wi-Fi (short for "Wireless Fidelity") relates to the name provided by the Wi-Fi Alliance, formerly WECA (Wireless Ethernet Compatibility Alliance). This group assures compatibility between hardware devices that use the 802.11 standards. Wi-Fi networks must comply with the 802.11a-x specifications.

Wi-Fi mesh [16] protocol IEEE 802.11s creates a mesh network that extends Wi-Fi coverage over a larger area and enhances overall network performance and reliability. Traditional Wi-Fi networks are based on a single wireless access point (router) communicating directly with Wi-Fi-enabled devices. They may suffer from limited range and dead zones in larger spaces.

A Wi-Fi mesh network consists of multiple interconnected access points that work together to create a seamless and continuous network. These access points, often referred to as "nodes" or "mesh nodes", communicate with each other wirelessly, forming a self-healing network that can automatically reroute data packets to find the most efficient path to reach the destination device.

The system architecture for WLAN mesh network technology is described in IEEE 802.11 functional requirements and scope [17] and illustrated in Figure 1.3.

The functional blocks of the architecture include the following:

• The Mesh Topology Learning, Routing, and Forwarding block includes a function for discovering neighbouring nodes, a function for obtaining radio metrics, which deliver information on the quality of wireless links,

Figure 1.3 Wi-Fi Mesh Layered Architecture

a routing protocol for determining routes to transfer packets to their destinations using MAC addresses as identifiers, and a packet forwarding function. The routing protocol must use radio metrics and multiple frequency channels according to radio conditions to efficiently use radio resources.

- The Mesh Network Measurement block includes functions for calculating radio metrics used by the routing protocol and measuring radio conditions within the WLAN mesh network for frequency channel selection.

- The Mesh Medium Access Coordination block contains functions for preventing degraded performance due to hidden and exposed terminals, procedures for performing priority control, congestion control, and admission control, and a function for achieving spatial frequency reuse.

- The Mesh Security block comprises security functions (e.g., WLAN security schemes defined by the IEEE 802.11 standard) for protecting data frames carried on the WLAN mesh network and management frames used by control functions such as routing protocol.

- The Interworking block implements the function that supports WLAN mesh network to conform to IEEE 802 network architecture and connect to other networks by implementing a transparent bridge function enforced in the mesh portal situated at the network boundary. Each WLAN mesh network must operate as a broadcast network to deliver forwarded packets to all terminals connected to the LANs.

- The Mesh Configuration and Management block comprises a WLAN interface for the automatic setting of each mesh point's RF parameters (transmit power, frequency channel selection, etc.) and quality of service (QoS) policy management.

Wi-Fi mesh protocol is designed to address the limitations of traditional Wi-Fi networks, making them ideal for large homes, offices, or public spaces where extended coverage and high-performance connectivity are required.

#### 1.3.5.6 Wi-SUN

Wi-SUN [18] stands for Wireless Smart Ubiquitous Network and is a mesh network protocol developed by Wi-SUN Alliance. Wi-SUN is one of the most popular IPv6 sub-GHz mesh technologies for smart utility and smart city applications. The target networks are named Field Area Networks (FANs), and they deliver a communications infrastructure for large-scale outdoor networks, usually outdoor IoT devices. FANs let industrial devices such as smart meters and streetlights interconnect onto one common network.

Wi-SUN is based on the IEEE 802.15.4g standard for the physical layer (PHY) and the IEEE 802.15.4e standard for the medium access control layer (MAC). It supports multiple data rates and frequency bands to meet regulatory requirements worldwide.

Wi-SUN makes interoperable, multi-service, secure wireless mesh networks available to service providers, utilities, municipalities/local governments, and other businesses. Wi-SUN can be used in various line-powered and battery-powered applications for large-scale outdoor IoT wireless communication networks. With the help of Wi-SUN, developers can add new features to existing infrastructure platforms by extending open standard internet protocols (IP) and APIs. With its long-range capabilities, high data throughput, and support for IPv6, Wi-SUN is designed to scale and makes wireless infrastructure easier for commercial applications and the development of smart cities.

#### 1.3.5.7 WirelessHART

WirelessHART [19][20] is a process automation application wireless communications protocol that provides wireless capabilities to extend Highway Addressable Remote Transducer (HART) by keeping compatibility with existing HART commands, tools, and devices.

The architecture of the WirelessHART protocol stack according to the OSI 7-layer communication model is illustrated in Figure 1.4.

The WirelessHART protocol stack addresses five layers: physical layer, data link/MAC layer, network layer, transport layer and application layer. A central network manager is added for arbitrating the communication schedule and manage the routing.

Figure 1.4 WirelessHART Protocol Architecture

WirelessHART uses mesh networking technology by design, where each device in a mesh network can act as a router for messages from other devices. This widens the range of the network and gives redundant communication routes to extend reliability in challenging radio environments encountered in process facilities [21][22][23]. Networks can scale up to 1000 nodes, but latency can be long and nondeterministic because transmissions occur only within an allocated time slot, and retransmissions are minimised.

Each WirelessHART network contains three major components:

- Wireless field devices that are connected to process or manufacturing equipment.

- Gateways that communicate among devices and on-premises host applications connected to high-speed backbone or other communications networks.

- A Network Manager configures the network, schedules communications between devices, monitors network health, and manages message routes. The Network Manager can be embedded into gateways, host applications, or process automation controllers.

# Plant Automation Network Field Device Field Router ((())) Device Device Router $(((\bullet)))$ Device Field Device Handheld Device Field Field Field Device Device Device

Plant Automation Application Host

# Figure 1.5 WirelessHART Mesh Networking